# ECET 310-001 Chapter 1 Concluded

W. Barnes, 9/2006, rev'd 9/07

Ref. Huang, Han-Way, The HCS12/9S12: An Introduction to Software and Hardware Interfacing, Thomson/Delmar.

# In this set of Slides:

- 1. Last of the Six Basic Addressing Modes

- 2. Introduction to Instructions

- Three Types of Move/Copy

- Add/Subtract

- 3. Instruction Execution & Queue

- 4. Three Simple Example Programs

### Six Basic Addressing Modes cont'd

- 6. Indexed, which has 5 basic sub-types

- 1. Constant (signed) offset (5, 9, 16 bits)

Idaa 10,x ; loads a with m[x+10]

2. <u>Indirect</u> constant <u>or</u> reg. D to create a POINTER to ADDRESS of operand Idaa [10,x] ; loads A with m[], which is <u>pointed to by</u> contents of m[x+10,11]& [x+11]

ex. If X = \$1000, M[\$1010 & \$1011] = \$20 & \$50, Then, A  $\leftarrow$  M[\$2050]

1. Auto pre OR post increment or decrement of index register (N.B. the number given with this type of addressing is the amount of incr or dec, not an offset)

Idaa 1,-SP ;decrements SP by 1 and then loads A staa 2, X+ ;stores A and then increments X by 2

#### **Questions:**

In #1, what determines if the offset is 5, 9, or 16 bits?

What distinguishes #2 from #1 above?

In #3, how can you indicate whether instruction executes or inc/decr first?

Indexed Addressing cont'd on next slide

## Sixth Basic Addressing Mode cont'd

[5 basic types of Indexed Mode cont'd]

### 4. Accumulator Offset Indexed Addressing

- The accumulator can be the 8-bit A or B or the 16-bit accumulator D.

- The base register can be X, Y, SP, or PC.

Idaa B,X ;loads A with m[B+X]

stab A,Y ;stores B in m[A+Y]

#### **Question:**

The **effective** address is the sum of the index register plus the unsigned number in the accumulator. Therefore, if X = 2A 04 and B = 4C in the first example, where in memory will the uctlr get the number to load into A?

## Sixth Basic Addressing Mode Concluded

[5 basic types of Indexed Mode concluded]

**5. Accumulator D Indirect Indexed Addressing** Value in D is added to the value in the base index register to form the address of the memory location that contains the address to the memory location affected by the instruction. Square brackets distinguish this addressing mode from accumulator D offset indexing (type #4, on previous slide).

#### Example using Computed GOTO

1. jmp [D,PC] ;D previously loaded with 0,2,or 4

2. go1 dc.w target1; note these assembler

3. go2 dc.w target2; directives store

4. go3 dc.w target3 : 2-byte addresses here

..

5. target1 ...

.

6. target2 ...

.

7. target3 ...

Suppose D = 4 on reaching jmp instruction, then 4 is added to PC, which will now point to go3 and thus target3 will be used in the jmp instruction. This results in the instructions starting at target3 to be executed.

Question: in line 2 of the example, how many labels are used and what are they?

## Introduction to Instructions

## What to keep in mind when using instructions:

How does the instruction affect registers and/or memory?

How does the instruction affect the CCR?

Is it clear where the input numbers are and where the results (destination) should go?

Is the program using signed numbers?

What kind of addressing modes are available for a particular instruction?

# Introduction to Instructions Cont'd., 3 basic types of move/copy:

- 1. Load / Store registers from / to memory

- updates the N and Z flags, clear V flag

- See table 1.4, p.19 (next slide)

- **Examples:** Idaa 0,X ; staa \$20 ; stx \$8000 ; Idd #100

- 2. Transfer, Exchange, Sign Extend (registers only)

- See table 1.5, p.20, (slide after next)

- Examples: tab; TAB, tfr A,X; exg D, X; sex A, X

- 3. Move (mem  $\leftrightarrow$  mem, I/O register  $\leftrightarrow$  mem)

- Also move immediate values into mem

- See table 1.6, p. 22 (second slide after next)

- **EXs:** movb #0, \$1500; movb \$100,\$800; movw 0,X, 0,Y

#### Questions:

How does the Appendix A show that flags are being changed (affected) by a load or store instruction?

How are memory and registers affected by the above examples?

Table 1.4 Load and store instructions

| Mnemonic           | Function                       | Operation                                |  |  |

|--------------------|--------------------------------|------------------------------------------|--|--|

| LDAA               | Load A                         | $(M) \Rightarrow A$                      |  |  |

| LDAB               | Load B                         | $(M) \Rightarrow B$                      |  |  |

| LDD                | Load D                         | $(M:M+1) \Rightarrow (A:B)$              |  |  |

| LDS                | Load SP                        | $(M:M+1) \Rightarrow SP$                 |  |  |

| LDX                | Load index register X          | $(M:M+1) \Rightarrow X$                  |  |  |

| LDY                | Load index register Y          | $(M:M+1) \Rightarrow X$                  |  |  |

| LEAS               | Load effective address into SP | Effective address $\Rightarrow$ SP       |  |  |

| LEAX               | Load effective address into X  | Effective address $\Rightarrow X$        |  |  |

| LEAY               | Load efective address into Y   | Effective address $\Rightarrow Y$        |  |  |

| Store Instructions |                                |                                          |  |  |

| Mnemonic           | Function                       | Operation                                |  |  |

| STAA               | Store A                        | $(A) \Rightarrow M$                      |  |  |

| STAB               | Store B                        | $(B) \Rightarrow M$                      |  |  |

| STD                | Store D                        | $(A) \Rightarrow M, (B) \Rightarrow M+1$ |  |  |

| STS                | Store SP                       | $(SP) \Rightarrow M, M+1$                |  |  |

| STX                | Store X                        | $(X) \Rightarrow M:M+1$                  |  |  |

| STY                | Store Y                        | $(Y) \Rightarrow M:M+1$                  |  |  |

Table 1.5, Xfer, Exchange, and Sign Extend Instructions

| Transfer       |                           |                                  |  |  |

|----------------|---------------------------|----------------------------------|--|--|

| TAB            | Xfer A to B               | (A) → B                          |  |  |

| ТВА            | Xfer B to A               | (B) <b>→</b> A                   |  |  |

| TAP            | Xfer A to CCR             | (A) → CCR                        |  |  |

| TPA            | Xfer CCR to A             | (CCR) → A                        |  |  |

| TFR src, obj   | Xfer reg. to reg.         | (src) → obj                      |  |  |

| TSX            | Xfer SP to X              | $(SP) \rightarrow X$             |  |  |

| TXS            | Xfer X to SP              | $(X) \rightarrow SP$             |  |  |

| TSY            | Xfer SP to Y              | $(SP) \rightarrow Y$             |  |  |

| TYS            | Xfer Y to SP              | (Y) → SP                         |  |  |

| Exchange       |                           |                                  |  |  |

| EXG reg1, reg2 | Exchange two registers    | $(A) \leftrightarrow (B)$ , etc. |  |  |

| XGDX           | Exchange X and D          | $(X) \leftrightarrow (D)$        |  |  |

| XGDY           | Exchange Y and D          | $(Y) \leftrightarrow (D)$        |  |  |

| Sign Extension |                           |                                  |  |  |

| SEX            | Sign extend 8-bit operand | (A,B,CCR) → X,Y, SP              |  |  |

Questions: In TAB, what happens to register A?

What is at least one difference between Load and Transfer instructions?

What is a difference between Transfer and Exchange instructions?

## **Move instructions**

(Used within memory, not registers, <u>but can</u> <u>also</u> use to move immediate number into memory)

Table 1.6 Move instructions

| Transfer Instructions |                                      |                                                          |  |  |

|-----------------------|--------------------------------------|----------------------------------------------------------|--|--|

| Mnemonic              | Function                             | Operation                                                |  |  |

| MOVB<br>MOVW          | Move byte (8-bit) Move word (16-bit) | $(M1) \Rightarrow M2$<br>$(M:M+1_1) \Rightarrow M:M+1_2$ |  |  |

## Introduction to Instructions cont'd

#### Add/Sub Instructions

- Destinations are a CPU register or accumulator.

- Three-operand ADD or SUB instructions always include the C flag as an operand and are used to perform multi-precision addition or subtraction

- See table 1.7, p.22 (next slide)

```

adca $1000 ; A ← [A] + [$1000] + C

suba $1002 ; A ← [A] - [$1002]

sbca $1000 ; A ← [A] - [$1000] - C

adda $1000 ; A ← [A] + [$1000]

```

Question: How can you change the second example to subtract the number \$44 from register A? What kind of addressing will be needed?

Table 1.7 Add and subtract instructions

| Add Instructions                            |                                                                                                                                                                      |                                                                                                                                                                                                                                 |  |  |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Mnemonic                                    | Function                                                                                                                                                             | Operation                                                                                                                                                                                                                       |  |  |

| ABA ABX ABY ADCA ADCB ADDA ADDB ADDD        | Add B to A Add B to X Add B to Y Add with carry to A Add with carry to B Add without carry to D | $(A) + (B) \Rightarrow A$ $(B) + (X) \Rightarrow X$ $(B) + (Y) \Rightarrow Y$ $(A) + (M) + C \Rightarrow A$ $(B) + (M) + C \Rightarrow B$ $(A) + (M) \Rightarrow A$ $(B) + (M) \Rightarrow B$ $(A:B) + (M:M+1) \Rightarrow A:B$ |  |  |

| Mnemonic                                    | Function                                                                                                                                                             | Operation                                                                                                                                                                                                                       |  |  |

| SBA<br>SBCA<br>SBCB<br>SUBA<br>SUBB<br>SUBD | Subtract B from A Subtract with borrow from A Subtract with borrow from B Subtract memory from A Subtract memory from B Subtract memory from D                       | $(A) - (B) \Rightarrow A$ $(A) - (M) - C \Rightarrow A$ $(B) - (M) - C \Rightarrow B$ $(A) - (M) \Rightarrow A$ $(B) - (M) \Rightarrow B$ $(D) - (M:M+1) \Rightarrow D$                                                         |  |  |

## Instruction Execution Cycle

- One or more read cycles to fetch instruction opcode bytes and addressing information

- One or more read cycles to fetch the memory operand (s) (optional)

- Perform the operation specified by the opcode

- One or more write cycles to write back the result to either a register or a memory location (optional)

## **Instruction Queue**

- The HCS12 executes one instruction at a time and many instructions take several clock cycles to complete.

- When the CPU is performing the operation, it does not need to access memory.

- The HCS12 prefetches instructions when the CPU is not accessing memory to speedup the instruction execution process.

- There are two 16-bit queue stages and one 16-bit buffer. Unless buffering is required, program information is first queued in stage 1, and then advanced to stage 2 for execution.

# Simple Example Programs (NOTE: see the Tracing Programs handout)

```

1. ;webex1, 8/4/06

2. ;program adds (- 50) to a number and stores result

equ -50; CE = -50

3. num

org $1800

4.

5. testval

db 60 : $3C = +60

6. answer rmb

7.

$2000

org

8.

ldaa

#num

9.

adda testval : -50 + 60 = 10 = $0A

10.

staa

answer

11_

SWI

12.

end

```

## Simple Example Programs Cont'd.

```

1. ;webex1a, 8/4/06

program adds (- 50) to a number and stores result

3. ; (revision of webex1 to use indexed addressing)

-50

4. num

equ

$1800

5.

org

6. testval

db 60

rmb 1

7. answer

reserve memory byte at answer

$2000

8.

org

9.

Idaa #num

10.

#testval

ldx

11.

#answer

ldy

12.

adda 0,x

13.

staa 0,y

14.

swi

15.

end

```

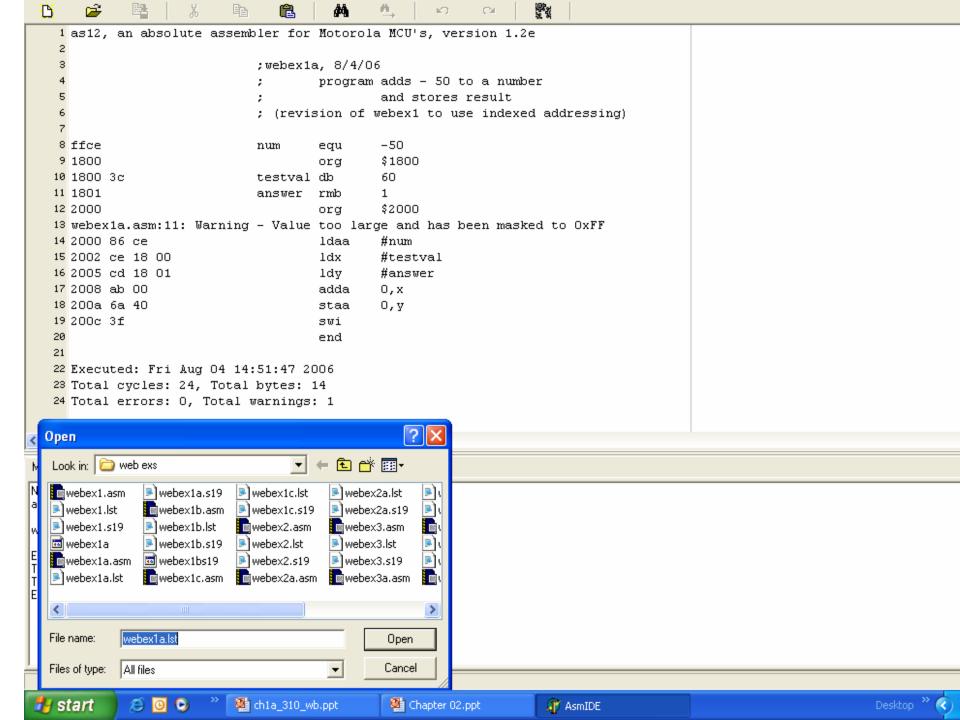

# Next Slide:

- a list file for webex1a

- inset showing list of <u>all</u> (asm, lst, s19) files in directory

# Simple Example Programs Cont'd.

```

1. ;webex1b, 8/4/06, program adds (- 50) to a number and stores result

; (revision of webex1 with a test for invalid results:

if result exceeds 8-bit limits for signed numbers

store FF in location [valid], otherwise store 00)

5. ; Program also includes a conditional branch

num

equ

-50

7.

$1800

org

8. testval

db

60

9. answer

rmb

;reserve memory byte at answer

10. valid

rmb

11.

$2000

orq

12.

valid

clr

:make default 00

13.

#num

ldaa

14.

adda testval

15.

good ;skip if results ok (checks overflow flag, table 2.2, p. 54)

bvc

16.

valid

:make FF

com

17. good

staa

answer

18.

swi

19.

end

```

# Simple Example Programs Cont'd.

```

1.

;webex1c, 9/13/06,;

program adds - 50 to a number and stores result

2.

; (revision of webex1 with a test for invalid results: see web1b for details)

; and use of indexed w/ normal and auto incr.

3.

4.

-50

equ

num

5.

$1800

org

6.

data

db

60, -200

7.

2

results

rmb

8.

valid

rmb

9.

$2000

orq

10.

:make default 00

clr

valid

11.

ldab

#num

12.

ldx

#data

13.

ldy

#results

14.

ldaa

1,x+

15.

aba

;add (-50) to first number

16.

;skip if results ok (overflow flag clear)

bvc

good

17.

#$FF, valid; otherwise ...

movb

18.

good

staa

1,y+

19.

Idaa 0,x

20.

;add (-50) to second number

aba

21.

;skip if results ok

bvc

good2

22.

#$FF, valid

movb

23.

good2

0,y

staa

24.

swi

25.

end

```